IL MODELLO VON NEUMANN

Stefano Petrarca

Conservatorio S. Cecilia - Roma

1 - Introduzione

La maggior parte dei sistemi di elaborazione elettronica che conosciamo adottano un'architettura basata sul cosiddetto modello Von Neumann; a grandi linee, tale modello può essere caratterizzato dai seguenti attributi:

A questo modello corrisponde un'architettura hardware/software che descriveremo nel prossimo paragrafo

2 - Architettura di un sistema Von Neumann

Come sappiamo, la macchina Von Neumann è un sistema uniprocessore che, in qualsiasi istante permette l'esecuzione di una e una sola istruzione. La fig. 1.1 mostra lo schema di un'architettura "convenzionale" in cui è possibile riconoscere una CPU, un singolo BUS,

una memoria centrale e un'insieme di interfacce denominato con I/O. Il BUS singolo (che è suddiviso in BUS indirizzi e BUS dati) permette alla CPU di accedere a una sola locazione di memoria o di I/O alla volta; la memoria, come già detto, è unica e condivide sia il codice che i dati. La CPU ha il compito di governare il flusso di esecuzione delle istruzioni sincronizzando tutte le parti del sistema a ciò preposte; nella CPU troviamo dei sotto-sistemi che svolgono funzioni diversificate come i registri, che consentono alla CPU di colloquiare con memoria e I/O,

l'unità di controllo (CU) che gestisce l'abilitazione o disabilitazione dei dispositivi del sistema durante l'esecuzione di un'istruzione, la ALU che realizza le operazioni aritmetiche e logiche e altri registri che fungono da interfaccia con il BUS. Come è noto, un'istruzione in linguaggio macchina, che spesso viene considerato come il più basso livello di programmazione, è suddivisa in azioni elementari di CPU nel cosiddetto micro-codice contenuto nella memoria di microprogramma che fa parte della CU; pertanto, quest'ultima eseguirà il micro-codice che non sarà altro che l'implementazione delle fasi di esecuzione di un'istruzione; più precisamente:

Ognuna di queste fasi avviene in un preciso istante di tempo scandito dal clock di sistema che provvede, quindi, alla sincronizzazione di tutte le attività; normalmente, ogni transizione del segnale di clock provoca un'azione da parte della CPU.

Infine, il blocco di I/O permette ai dispositivi periferici (tastiera, video, stampante, unità a disco) di interfacciarsi al BUS in modo che la CPU possa riferirsi ad essi come se fossero delle locazioni di memoria.

3 - Estensione del modello e miglioramento delle prestazioni

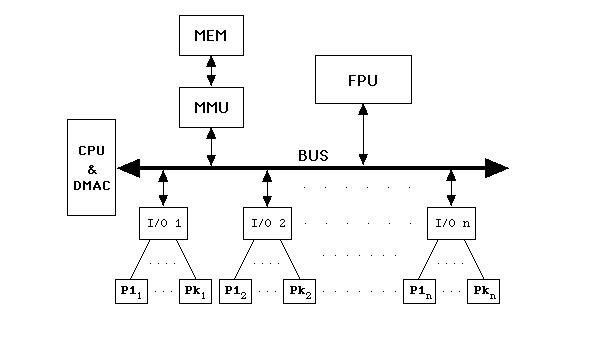

Il dialogo tra CPU e I/O, così come è stato descritto nel precedente paragrafo, avviene a controllo di programma; la CPU, quindi, nel caso che un dispositivo periferico segnali (ad esempio tramite interrupt) la necessità di servizio, provvederà, tramite opportuno programma driver, a scambiare dati con il dispositivo richiedente. Se il dispositivo ha bisogno di un servizio rapido e grossi blocchi di dati da scambiare, questa modalità di interfacciamento risulta alquanto inefficiente. Pertanto, è preferibile usare una modalità di accesso diretto in memoria (DMA, Direct Memory Access) che permette al dispositivo di I/O di scambiare dati direttamente con la memoria senza passare attraverso la CPU; a ogni unità di I/O è assegnato un canale di DMA in modo che i dispositivi periferici possano compiere le loro operazioni concorrentemente. Un controllore di DMA gestirà le operazioni di scambio in modo che, se un dispositivo di I/O deve trasferire dati da o verso la memoria, provvederà a comunicare la richiesta di rilascio del BUS alla CPU che risponderà affermativamente quando è pronta; in questo caso, la CPU metterà i registri di interfacciamento col BUS in alta impedenza permettendo al controllore di DMA di acquisire il possesso del BUS; a questo punto il DMAC genererà la sequenza di indirizzi dell'area di memoria dedicata al trasferimento dei dati con la periferica in questione. In fig. 1.2 è mostrato lo schema un'architettura classica allargata.

fig. 1.2 - Architettura Von Neumann allargata

Nello schema di fig. 1.2 sono mostrate altre due unità che lavorano concorrentemente con il processore centrale: la MMU (Memory Management Unit), che si occupa della generazione degli indirizzi fisici sulla base di quelli logici espressi dal programma, e la FPU (Floating Point Unit) che provvede al calcolo matematico in virgola mobile.

Questo approccio consente al sistema di effettuare alcune operazioni in parallelo in in modo da aumentarne le prestazioni. Mette in evidenza, altresì, i limiti del modello Von Neumann; in particolare il vero collo di bottiglia di quest'architettura è l'esistenza di un singolo BUS dimodoché, qualsiasi trasferimento dati su questo canale di comunicazione sarà effettuato sequenzialmente, una parola alla volta. Per gestire efficientemente attività parallele si dovrà andare verso un superamento dell'architettura convenzionale.